MITSUBISHI(MICMPTR/MIPRC)

T-51-19

PROGRAMMABLE INTERVAL TIMER

#### DESCRIPTION

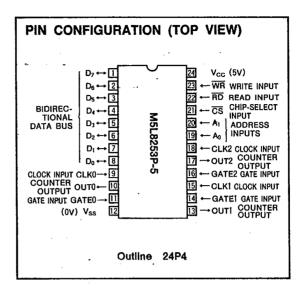

The M5L8253P-5 is a programmable general-purpose timer device developed by using the N-channel silicon-gate ED-MOS process. It offers counter and timer functions in systems using an 8-bit parallel-processing CPU.

The use of the M5L8253P-5 frees the CPU from the execution of looped programs, count-operation programs and other simple processing involving many repetitive operations, thus contributing to improved system throughputs.

The M5L8253P-5 works on a single power supply, and both its input and output can be connected to a TTL circuit.

#### **FEATURES**

- Single 5V supply voltage

- TTL compatible

- Clock period: DC~2,6MHz

- 3 independent built-in 16-bit down counters

- 6 counter modes freely assignable for each counter

- Binary or decimal counts

#### **APPLICATION**

Delayed-time setting, pulse counting and rate generation in microcomputers.

#### **FUNCTION**

Three independent 16-bit counters allow free programming based on mode-control instructions from the CPU. When roughly classified, there are 6 modes (0 $\sim$ 5). Mode 0 is mainly used as an interruption timer and event counter, mode 1 as a digital one-shot, modes 2 and 3 as a rate generator, mode 4 for a software triggered strobe, and mode 5 for a

hardware triggered strope. The count can be monitored and set at any time. The counter operates with either the binary or BCD system.

## MITSUBISHI (MICMPTR/MIPRC)

T-51-19

PROGRAMMABLE INTERVAL TIMÈR

#### **DESCRIPTION OF FUNCTIONS**

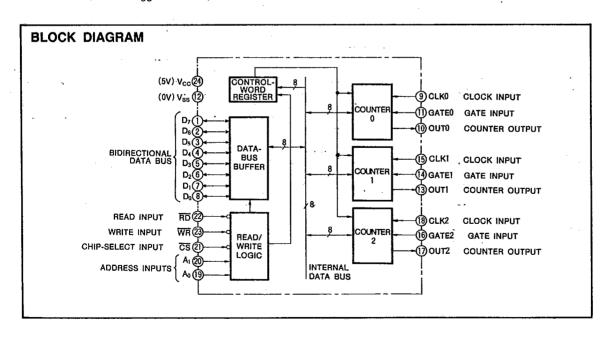

#### **Data-Bus Buffer**

This 3-state, bidirectional, 8-bit buffer is used to interface the M5L8253P-5 to the system-side data bus. Transmission and reception of all the data including control words for mode designation and values written in, and read from, the counters are carried out through this buffer.

#### Read/Write Logic

The read/write logic accepts control signals  $(\overline{RD}, \overline{WR})$  from the system and generates control signals for each counter. It is enabled or disabled by the chip-select signal  $(\overline{CS})$ ; if  $\overline{CS}$  is at the high-level the data-bus buffer enters a floating (high-impedance) state.

#### Read Input (RD)

The count of the counter designated by address inputs  $A_0$  and  $A_1$  on the low-level is output to the data bus.

#### Write Input (WR)

Data on the data bus is written in the counter or control-word register designated by address inputs  $A_0$  and  $A_1$  on the low-level.

### Address inputs (A<sub>0</sub>, A<sub>1</sub>)

These are used for selecting one of the 3 internal counters and either of the control-word registers.

#### Chip-Select Input (CS)

A low-level on this input enables the M5L8253P-5. Changes in the level of the  $\overline{\text{CS}}$  input have no effect on the operation of the counters.

#### **Control-Word Register**

This register stores information required to give instructions about operational modes and to select binary or BCD counting. Unlike the counters, it allows no reading, only writing.

#### Counters 0.1 and 2

These counters are identical in operation and independent of each other. Each is a 16-bit, presettable, down counter, and has clock-input, gate-input and output pins. The counter can operate in either binary or BCD using the falling edge of each clock. The mode of counter operation and the initial value from which to start counting can be designated by software. The count can be read by input instruction at any time, and there is a "read-on-the-fly" function which enables stable reading by latching each instantaneous count to the registers by a special counter-latch instruction.

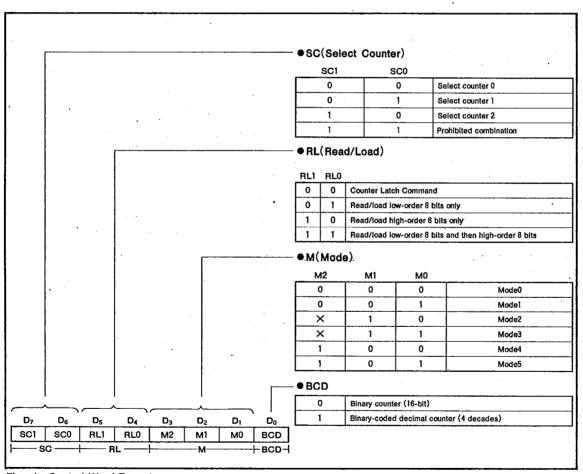

#### CONTROL WORD AND INITIAL-VALUE LOADING

The function of the M5L8253P-5 depends on the system software. The operational mode of the counters can be specified by writing control words  $(A_0, A_1 = 1, 1)$  into the control-word registers.

The programmer must write out to the M5L8253P-5 the programmed number of count register bytes (1 or 2) prior to actually using the selected counter.

Fig. 1 shows control-word format, which consists of 4 fields. Only the counter selected by the  $D_7$  and  $D_6$  bits of the control word is set for operation. Bits  $D_5$  and  $D_4$  are used for specifying operations to read values in the counter and to initialize. Bits  $D_3 \sim D_1$  are used for mode designation, and  $D_0$  for specifying binary or BCD counting. When  $D_0 = 0$ , binary counting is employed, and any number from  $0000_{16}$  to FFFF $_{16}$  can be loaded into the count register. The counter is counted down for each clock. The counting of  $0000_{16}$  causes the transmission of a time-out signal from the count-output pin.

The maximum number of counts is obtained when  $0000_{16}$  is set as the initial value. When  $D_0 = 1$ , BCD counting is employed, and any number from  $0000_{10}$  to  $9999_{10}$  can be loaded on the counter.

Neither system resetting nor connecting to the power supply sets the control word to any specific value. Thus to bring the counters into operation, the above-mentioned control words for mode designation must be given to each counter, and then 1~2 byte initial counter values must be set. The following is an example of this programming step.

To designate mode 0 for counter 1, with initial value  $8253_{16}$  set by binary count, the following program is used:

| MVI | A, 70 <sub>15</sub> | Control word 70 <sub>16</sub>                   |

|-----|---------------------|-------------------------------------------------|

| OUT | n <sub>1</sub>      | n <sub>1</sub> is control-word-register address |

| MVI | A, 53 <sub>15</sub> | Low-order 8 bits                                |

| OUT | n <sub>2</sub>      | n <sub>2</sub> is counter 1 address             |

| MVI | A, 82 <sub>16</sub> | High-order 8 bits                               |

| OUT | n <sub>2</sub>      | n <sub>2</sub> is counter 1 address             |

Thus, the program generally has the following sequence:

- (1) Control-word output to counter i (i=0, 1, 2).

- (2) Initialization of low-order 8 counter bits

- (3) Initialization of high-order 8 counter bits

The three counters can be executed in any sequence. It is possible, for instance, to designate the mode of each counter and then load initial values in a different order. Initialization of the counters designated by RL 1 and RL 0 must be executed in the order of the low-order 8 bits and then the high-order 8 bits for the counter in question.

### MITSUBISHI (MICMPTR/MIPRC)

# PROGRAMMABLE INTERVAL TIMER

Table 1 Basic Functions

| <u>cs</u> | RD | WR | A <sub>1</sub> | A <sub>0</sub> | Function                       |

|-----------|----|----|----------------|----------------|--------------------------------|

| Ł.        | Н  | L  | 0.             | 0              | Data bus→Counter 0             |

| L         | н  | L  | 0              | 1 1            | Data bus→Counter 1             |

| Ļ         | н  | L  | 1              | 0              | Data bus→Counter 2             |

| L         | н  | L  | 1              | 1 1            | Data bus→Control-word register |

| L         | L  | н  | 0              | 0              | Data bus←Counter 0             |

| · L       | L  | н  | 0              | 1 1            | Data bus←Counter 1             |

| L         | L  | н  | 1              | 0 -            | Data bus←Counter 2             |

| L         | L  | Н  | 1              | ļ 1 ļ          | 3-state                        |

| , н       | ×  | ×  | ×              | . ×            | 3-state                        |

| L         | н  | н  | ×              | ×              | 3-state                        |

Fig. 1 Control-Word Format

T-51-19

## MITSUBISHI(MICMPTR/MIPRC)

PROGRAMMABLE INTERVAL TIMER

#### MODE DEFINITION

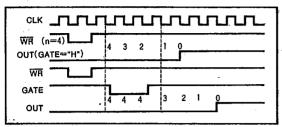

#### Mode 0 (Interrupt on Terminal Count)

Mode set and initialization cause the counter output to go low-level (see Fig. 2). When the counter is loaded with an initial value, it will start counting the clock input. When the terminal count is reached, the output will go high-level and remain high-level until the selected count register is reloaded with the mode. This mode can be used when the CPU is to be interrupted after a certain period or at the time of counting up.

Fig. 2 shows a setting of 4 as the initial value. If gate input goes low-level, counting is inhibited for the duration of the low-level period.

Reloading of the initial value during count operation will stop counting by the loading of the first byte and start the new count by the loading of the second byte.

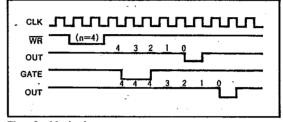

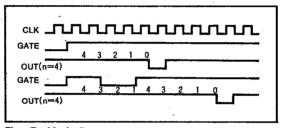

#### Mode 1 (Programmable One-Shot)

The gate input functions as a trigger input. A gate-input rising edge causes the generation of low-level one-shot output with a predetermined clock length starting from the next clock. Fig. 3 shows an initial setting of 4. While the counter output is at the low-level (during one-shot), loading of a new value does not change the one-shot pulse width, which has already been output. The current count can be read at any time without affecting the width of the one-shot pulse being output. This mode permits retriggering.

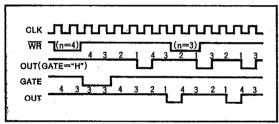

#### Mode 2 (Rate Generator)

Low-level pulses during one clock operation are generated from the counter output at a rate of one per n clock inputs (where n is the value initially set for the counter). When a new value is loaded during the counter operation, it is reflected on the output after the pulses by the current count have been output. In the example shown in Fig. 4, n is given as 4 at the outset and is then changed to 3.

In this mode, the gate input provides a reset function. While it is on the low-level, the output is maintained high-level; the counter restarts from the initial value, triggered by a rising gate-input edge. This gate input, therefore, makes possible external synchronization of the counter by hardware.

After the mode is set, the counter does not start counting until the rate n is loaded into the count register, with the counter output remaining at the high-level.

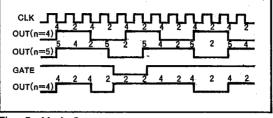

#### Mode 3 (Square Rate Generator)

This is similar to Mode 2 except that it outputs a square wave with the half count of the set rate. When the set value n is odd, the square-wave output will be high for (n+1)/2 clock-input counts and low-level for (n-1)/2 counts. When a new rate is reloaded into the count register during its operation, it is immediately reflected on the count directly following the output transition (high-to-low or low-to-high) of the current count. Gate-input operations are exactly the same as in Mode 2. Fig. 5 shows an example of Mode 3 operation.

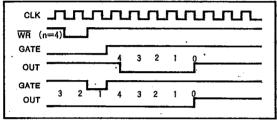

#### Mode 4 (Software Triggered Strobe)

After the mode is set, the output will be high-level. By loading a number on the counter, however, clock-input counts can be started and on the terminal count, the output will go low for one input-clock period and then will go high again. Mode 4 differs from Mode 2 in that pulses are not output repeatedly with the same set count. The pulse output is delayed one clock period in Mode 2, as shown in Fig. 6. When a new value is loaded into the count register during its count operation, it is reflected on the next pulse output without affecting the current count. The count will be inhibited while the gate input is low-level.

#### Mode 5 (Hardware Triggered Strobe)

This is a variation of Mode 1. The gate input provides a trigger function, and the count is started by its rising edge. On the terminal count, the counter output goes low for on one clock period and then goes high-level. As in Mode 1, retriggering by the gate input is possible. An example of timing in Mode 5 is shown in Fig. 7.

As mentioned above, the gate input plays different roles according to the mode. The functions are summarized in Table 2.

Table 2 Gate Operations

| Gate | Low-level<br>of<br>going low-level                            | Rising                                                          | High-level          |

|------|---------------------------------------------------------------|-----------------------------------------------------------------|---------------------|

| 0    | Disables counting                                             |                                                                 | Enables counting    |

| 1    |                                                               | (1) Initiates counting<br>(2) Resets output<br>after next clock | -                   |

| 2    | (1) Disables counting<br>(2) Sets output high<br>immediately  | (1) Reloads counter<br>(2) Initiates counting                   | Enables<br>counting |

| 3    | (1) Disables counting<br>(2) Sets output high.<br>immediately | (1) Reloads counter<br>(2) Initiates counting                   | Enables<br>counting |

| 4    | Disables counting                                             |                                                                 | Enables<br>counting |

| 5    |                                                               | Initiates counting                                              |                     |

## MITSUBISHI(MICMPTR/MIPRC)

M5L8253P-5

T-51-19

PROGRAMMABLE INTERVAL TIMÈR

Fig. 2 Mode 0

Fig. 5 Mode 3

Fig. 3 Mode 1

Fig. 6 Mode 4

Fig. 4 Mode 2

Fig. 7 Mode 5

#### **COUNTER MONITORING**

Sometimes the counter must be monitored by reading its count or using it as an event counter. The M5L8253P-5 offers the following two methods for count reading:

#### Read Operation

The count can be read by designating the address of the counter to be monitored and executing a simple I/O read operation. In order to ensure correct reading of the count, it is necessary to cause the clock input to pause by external logic or prevent a change in the count by gate input. An example of a program to read the counter 1 count is shown below. If RL1, RL0=1, 1 has been specified in the control word, the first IN instruction enables the low-order 8 bits to be read and the second IN instruction enables the high-order 8 bits.

IN n<sub>2</sub> ···· n<sub>2</sub> is the counter 1 address

MOV D, A IN n<sub>2</sub>

E. A

MOV

The IN instruction should be executed once or twice by the RL1 and RL0 designations in the control-word register.

#### Read-on-the-Fly Operation

This method makes it possible to read the current count without affecting the count operation at all. A special counter-latch command is first written in the control-word register. This causes latching of all the instantaneous counts to the register, allowing retention of stable counts. An example of a program to execute this operation for counter 2 is given below.

MVI A, 1000XXXX ····  $D_5 = D_4 = 0$  designates counter latching

OUT  $n_1 \cdot \cdot \cdot \cdot n_1$  is the control-word-register address

IN  $n_3 \cdot \cdot \cdot \cdot n_3$  is the counter 2 address

MOV D, A

IN  $n_3$ MOV E. A

In this example, the IN instruction is executed twice. Due to the internal logic of the M5L8253P-5 it is absolutely essential to complete the entire reading procedure. If 2 bytes are programmed to be read, then two bytes must be read before any OUT instruction can be executed to the same counter.

## MITSUBISHI(MICMPTR/MIPRC)

## PROGRAMMABLE INTERVAL TIMER

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                                                      | Conditions                      | Ratings        | Unit |

|------------------|----------------------------------------------------------------|---------------------------------|----------------|------|

|                  | Power supply voltage                                           |                                 | -0.5~7         | ٧    |

| Voo              |                                                                | With respect to V <sub>SS</sub> | -0.5~7         | V    |

| Vı               | Input voltage                                                  |                                 | -0.5~7         | V    |

| V <sub>o</sub>   | Output voltage                                                 | Ta=25°C                         | 1000           | mW   |

| Pd               | Maximum power dissipation                                      | 1a 25 0                         | -20~75         | င    |

|                  |                                                                |                                 | -65~150        | ా    |

| T <sub>opr</sub> | Operating free-air temperature range Storage temperature range |                                 | <b>−65~150</b> |      |

## RECOMMENDED OPERATING CONDITIONS (Ta=-20~75°C, unless otherwise noted)

|        |                      |     | Unit |     |      |

|--------|----------------------|-----|------|-----|------|

| Symbol | Parameter            | Min | Nom  | Max | Olik |

| Voc    | Power supply voltage | 4.5 | 5    | 5.5 | ٧    |

| Vss    | Supply voltage (GND) |     | 0    |     | V    |

## **ELECTRICAL CHARACTERISTICS** ( $T_a = -20 \sim 75 \, \text{C}$ , $V_{cc} = 5 \, \text{V} \pm 10 \, \text{M}$ , $V_{ss} = 0 \, \text{V}$ , unless otherwise noted)

|            |                                   |                                                                           |      |     | 1.1-14  |      |

|------------|-----------------------------------|---------------------------------------------------------------------------|------|-----|---------|------|

| Symbol     | Parameter                         | Parameter Test conditions                                                 | Min  | Тур | Max     | Unit |

| ViH        | High-level input voltage          |                                                                           | 2,2  |     | Vcc+0.5 | v    |

| VIL        | Low-level input voltage           |                                                                           | -0.5 |     | 0.8     |      |

| VoH        | High-level output voltage         | I <sub>OH</sub> =-400μA                                                   | 2.4  |     |         | ٧    |

| Vol        | Low-level output voltage          | I <sub>OL</sub> =2.2mA                                                    |      |     | 0.45    | ٧    |

| lin.       | High-level input current          | V <sub>I</sub> =V <sub>CC</sub>                                           |      |     | ±10     | μA   |

| h <u>.</u> | Low-level input current           | V <sub>1</sub> =0V                                                        |      |     | ±10     | μA   |

| loz        | Off-state output current          | Vo=0V~Vcc                                                                 |      |     | ±10     | μА   |

| loa.       | Supply current from Vcc           | V <sub>SS</sub> =0V                                                       |      |     | 140     | mA   |

| Cı         | Input terminal capacitance        | V <sub>IL</sub> =V <sub>SS</sub> , f=1MHz, 25mVrms, T <sub>a</sub> =25°C  |      |     | 10      | pF   |

| Ciro       | Input/output terminal capacitance | V <sub>I/OL</sub> =V <sub>SS</sub> , f=1MHz,25mVrms, T <sub>a</sub> =25°C |      |     | 20      | pF   |

MITSUBISHI (MICMPTR/MIPRC)

## PROGRAMMABLE INTERVAL TIMER

## TIMING REQUIREMENTS ( $\tau_a$ =-20~75°C, $V_{cc}$ = 5 V±10%, $V_{ss}$ = 0 V, unless otherwise noted)

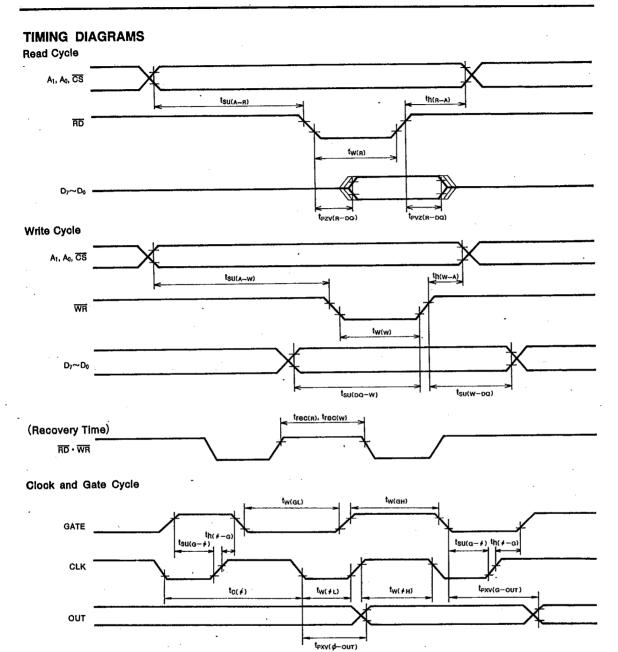

#### Read cycle

| Symbol            | Parameter                      | Test conditions  |      |     |     |      |

|-------------------|--------------------------------|------------------|------|-----|-----|------|

| Cynnbor           | raianoto                       | 1 est conditions | Min  | Тур | Max | Unit |

| t <sub>W(B)</sub> | Read pulse width               |                  | 300  |     |     | ns   |

| tsu(A-R)          | Address setup time before read | ]                | 30   |     |     | ns   |

| th(n-A)           | Address hold time after read   |                  | 5    | ,   |     | ns   |

| trec(R)           | Read recovery time             | 1                | 1000 |     |     | ns.  |

#### Write cycle

| Symbol               | Parameter                       | Test conditions |      |     |     |      |

|----------------------|---------------------------------|-----------------|------|-----|-----|------|

| Syllibol             | Falamoto                        | Test conditions | Min  | Тур | Max | Unit |

| tw(w)                | Write pulse width               | -               | 300  |     |     | ns   |

| t <sub>SU(A-W)</sub> | Address setup time before write |                 | 30   |     |     | , ns |

| th(w-A)              | Address hold time after write   |                 | 30   |     |     | ns   |

| tsu(pa-w)            | Data setup time before write    |                 | 250  |     |     | ns   |

| th(w-pa)             | Data hold time after write      |                 | 30   | ·   |     | ns   |

| trec(w)              | Write recovery time             | •               | 1000 |     |     | ns   |

#### Clock and gate timing

| Occasio al        |                              | Took conditions |     | Limits |     | 11-14 |

|-------------------|------------------------------|-----------------|-----|--------|-----|-------|

| Symbol            | Parameter                    | Test conditions | Min | Тур    | Max | Unit  |

| tw(≠H)            | Clock high pulse width       |                 | 230 |        |     | ns    |

| tw(≠L)            | Clock low pulse width        | ]               | 150 |        |     | ns    |

| t <sub>G(≠)</sub> | Clock cycle time             |                 | 380 |        | DC  | ns    |

| tw(an)            | Gate high pulse width        |                 | 150 |        |     | sn    |

| tw(gL)            | Gate low pulse width         | ]               | 100 |        |     | ns    |

| tsu(a-+)          | Gate setup time before clock | ] .             | 100 |        |     | ns    |

| th( #-a)          | Gate hold time after clock   |                 | 50  |        |     | ns    |

#### SWITCHING CHARACTERISTICS ( $T_a=-20\sim75$ °C, $V_{cc}=5$ V $\pm10\%$ , $V_{ss}=0$ V, unless otherwise noted)

| Symbol      | Parameter                                              | Test conditions |     | Unit |                                 |      |

|-------------|--------------------------------------------------------|-----------------|-----|------|---------------------------------|------|

|             | Falanielei                                             | rest conditions | Min | Тур  | Max<br>200<br>100<br>300<br>400 | Onit |

| tezv(R·DQ)  | Propagation time from read to output                   |                 |     |      | 200                             | ns   |

| tpvz(R-DQ)  | Propagation time from read to output floating (Note 2) | 0 150 5         | 25  |      | 100                             | ns   |

| tpxv(a-our) | Propagation time from gate to output                   | C∟=150pF        |     |      | 300                             | ns   |

| tpxv(#-out) | Propagation time from clock to output                  |                 |     |      | 400                             | ns   |

Note 1: A.C Testing waveform

Input pulse level Input pulse lever

Input pulse rise time

Input pulse fall time

Reference level input

output

2: Test condition is not applied 0.45~2.4V 20ns 20ns

V<sub>IH</sub>=2, 2V, V<sub>IL</sub>=0, 8V V<sub>OH</sub>=2, 0V, V<sub>OL</sub>=0, 8V

Input

Output

MITSUBISHI LSIs

## M5L8253P-5

MITSUBISHI(MICMPTR/MIPRC)

T-51-19

PROGRAMMABLE INTERVAL TIMER